- 您现在的位置:买卖IC网 > Sheet目录323 > EK-K7-KC705-CES-G-J (Xilinx Inc)KINTEX-7 FPGA KC705 EVAL KIT

�� �

�

�

�Kintex-7� FPGAs� Data� Sheet:� DC� and� AC� Switching� Characteristics�

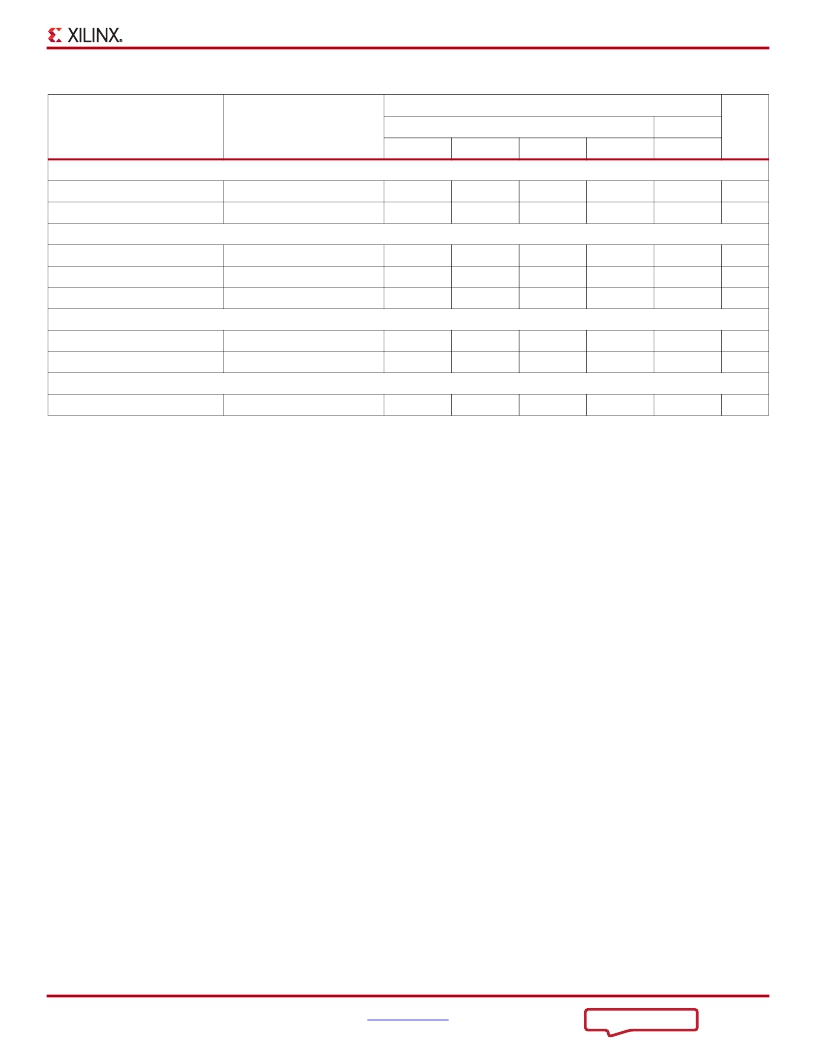

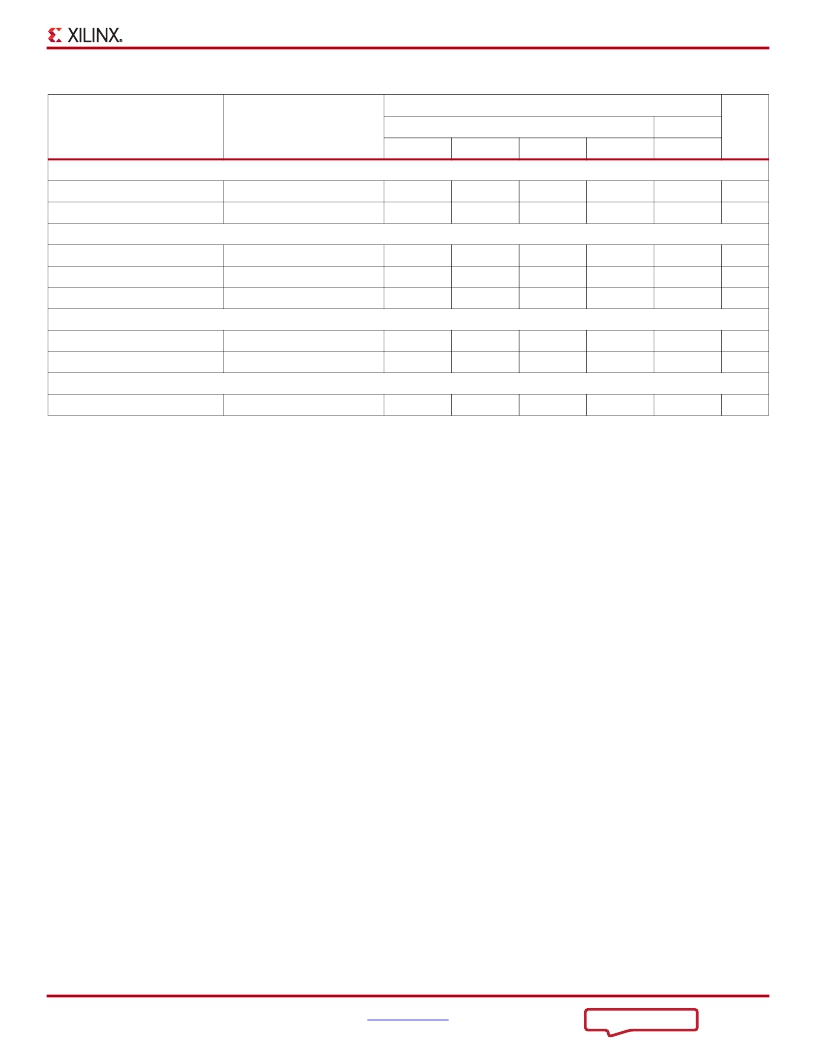

�Table� 28:� IO_FIFO� Switching� Characteristics�

�Speed� Grade�

�Symbol�

�Description�

�1.0V�

�0.9V�

�Units�

�-3�

�-2/-2L�

�-1�

�-1M�

�-2L�

�IO_FIFO� Clock� to� Out� Delays�

�T� OFFCKO_DO�

�T� CKO_FLAGS�

�RDCLK� to� Q� outputs�

�Clock� to� IO_FIFO� Flags�

�0.51�

�0.59�

�0.56�

�0.62�

�0.63�

�0.81�

�0.63�

�0.81�

�0.81�

�0.77�

�ns�

�ns�

�Setup/Hold�

�T� CCK_D� /T� CKC_D�

�D� inputs� to� WRCLK�

�0.43/–0.01� 0.47/–0.01� 0.53/–0.01�

�0.53/0.09�

�0.76/–0.05�

�ns�

�T� IFFCCK_WREN� /T� IFFCKC_WREN�

�WREN� to� WRCLK�

�0.39/–0.01� 0.43/–0.01� 0.50/–0.01� 0.50/–0.01� 0.70/–0.05�

�ns�

�T� OFFCCK_RDEN� /T� OFFCKC_RDEN�

�RDEN� to� RDCLK�

�0.49/0.01�

�0.53/0.02�

�0.61/0.02�

�0.61/0.02�

�0.79/–0.02�

�ns�

�Minimum� Pulse� Width�

�T� PWH_IO_FIFO�

�T� PWL_IO_FIFO�

�RESET,� RDCLK,� WRCLK�

�RESET,� RDCLK,� WRCLK�

�0.81�

�0.81�

�0.92�

�0.92�

�1.08�

�1.08�

�1.08�

�1.08�

�1.29�

�1.29�

�ns�

�ns�

�Maximum� Frequency�

�F� MAX�

�RDCLK� and� WRCLK�

�533.05�

�470.37�

�400.00�

�400.00�

�333.33�

�MHz�

�DS182� (v2.8)� March� 4,� 2014�

�Product� Specification�

���29�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

EK-S6-SP601-G

KIT EVAL SPARTAN 6 SP601

EK-S6-SP605-G

KIT EVAL SPARTAN 6 SP605

EK-V6-ML631-G-J

VIRTEX-6 HXT FPGA ML631 EVAL KIT

EK-V7-VC707-CES-G

VIRTEX-7 VC707 EVAL KIT

EK-Z7-ZC702-CES-G

ZYNQ-7000 EPP ZC702 EVAL KIT

EL1848IYZ-T7

IC LED DRIVR WHITE BCKLGT 8-MSOP

EL7156CSZ

IC DRIVER PIN 40MHZ 3STATE 8SOIC

EL7158ISZ

IC DVR PIN 40MHZ 3STATE 8-SOIC

相关代理商/技术参数

EK-K7-KC705-G

制造商:Xilinx 功能描述:KINTEX-7 FPGA KC705 EVALUATION KIT 制造商:Xilinx 功能描述:KINTEX-7 FPGA KC705 EVALUATION KIT - Boxed Product (Development Kits) 制造商:Xilinx 功能描述:KINTEX-7 FPGA KC705 EVAL KIT

EK-K7-KC705-G-J

制造商:Xilinx 功能描述:KINTEX-7 FPGA KC705 EVAL KIT

EKK8011

制造商:未知厂家 制造商全称:未知厂家 功能描述:USB + PS/2 keyboard controller

EKK8011AB

制造商:EMC 制造商全称:ELAN Microelectronics Corp 功能描述:USB & PS/2 Keyboard Encoder

EKK8301

制造商:未知厂家 制造商全称:未知厂家 功能描述:PS/2 keyboard controller

EKK-EVALBOT

功能描述:开发板和工具包 - ARM Keil Stellaris Eval Robot

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V

EKK-LM3S1968

功能描述:开发板和工具包 - ARM Stellaris Eval Kit w/ ARM/Keil Tools RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V

EKK-LM3S1968

制造商:Texas Instruments 功能描述:LM3S1968 MCU Eval Kit w/ Keil RealView M